PAGE CONTENTS

Objectives

Architecture of Thales Alenia Space future avionics as well as methods and tools for its development, integration and verification will be specified during this project. This includes:

OBC-core specification with its variability to cope with various missions needs including LEO, MEO, GEO and interplanetary exploration missions. And:

For Hardware:

- OBC-D modules specification.

- OBC-D Design Description and Design Report.

- OBC-D test and validation plan.

- OBC-D tests and test bench specification.

- OBC-D Elegant Bread-Board specification.

For FPGA fabric:

- Market and heritage survey.

- IPs functions and interfaces specification.

- FPGA bit-stream development.

For Boot and Hardware Dependent Software:

- Boot Software specification.

- Software drivers for FPGA functions interfacing specification.

- Development of test equipment for IPs and IP-drivers integration and test.

For Application Software:

- Selection of ARM multi-core RTOS (Real Time Operating System).

- Overall software architecture definition.

- RTOS and software prototype integration and test.

For Avionics:

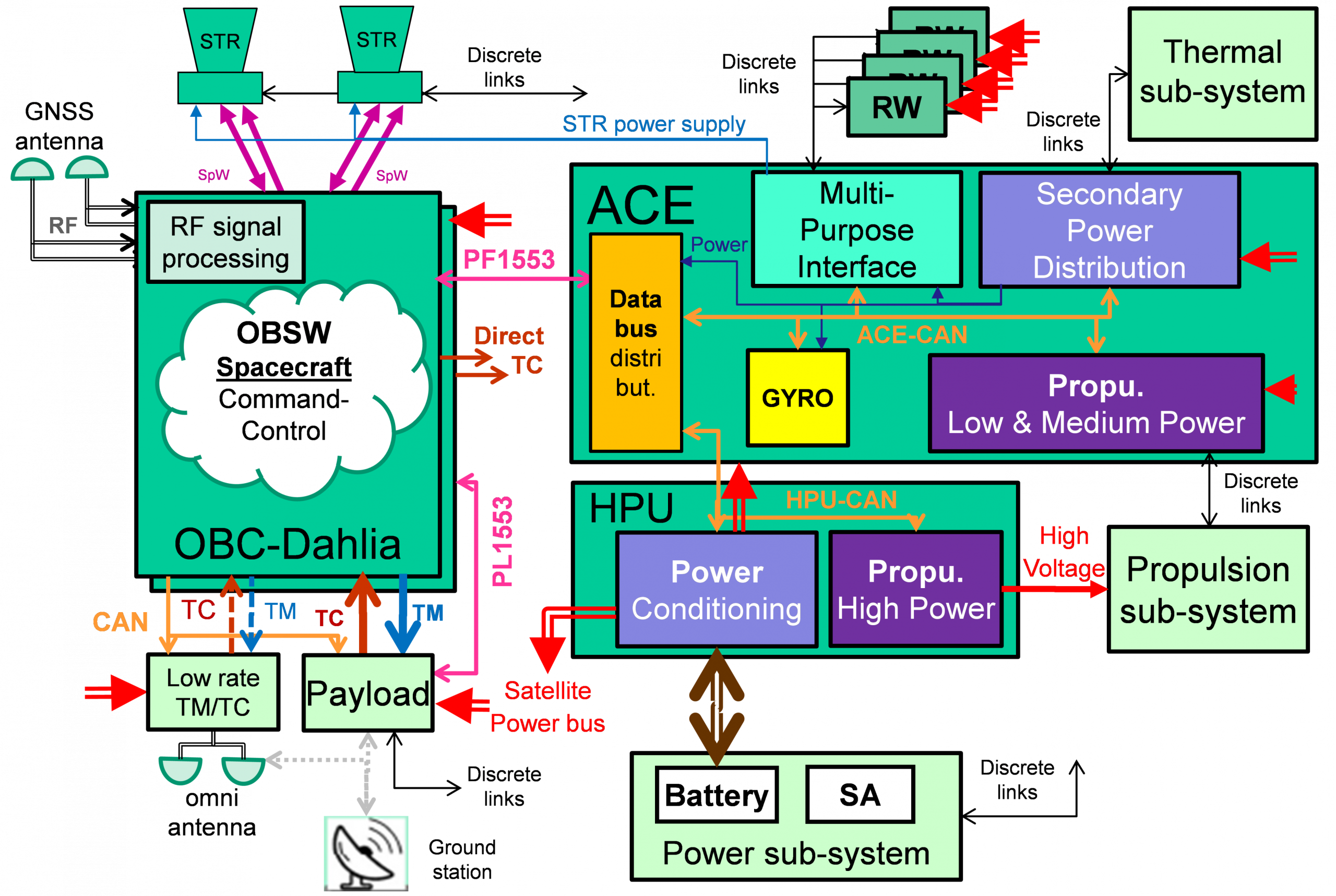

- Specification of avionics interfaces insured by the Avionics Centralized Electronics.

- OBSW Execution Platform and Equipment management Specification.

- Avionics development and validation plan.

- Avionics Tests and test bench specification.

- First test bench prototype development.

The overall study is accompanied by product assurance and quality for:

- Critical Item List and Qualification Status List.

- OBC-D reliability assessment and FMEA.

Challenges

One challenge of this study consists in defining the development logic for this new generation computer while following the NG-ULTRA SoC development in parallel to activities for definition and validation of Avionics, Hardware, IPs, Software and ACE.

In addition, the NG-ULTRA offers a high computing power together with very large FPGA capacity interconnected through high speed AMBA bus. Functions insured by several chips in the current platform computers can hence be integrated on a single chip allowing significant cost saving.

Functions allocation among Hardware, FPGA and Software while keeping good dependability level represents one the main challenge of the study.

System Architecture

Refer to Product features.

Plan

Main project milestones are:

- Kick-Off meeting on 2020 Feb 14th with presentation of performed work including preliminary specification for OBC-D, FPGA IPs and Low Level Software.

- Milestone 1 on 2020 March 19th for preliminary specification review.

- Milestone 2 to reach PDR level for OBC-D equipment is split in 3 parts.

- Part1 held on 2020 May 28th for review of updated specification, reliability assessment and FMEA, test plan and test equipment specification.

- Part2 held on 2020 July 23rd, for review of updated documentation and detailed specification.

- Completion foreseen in 2020 September.

Current Status

The complete set of documentation is available with a few exceptions that will be delivered for Milestone 2 completion.

Main achievements:

- OBC-D HW: EBB manufacturing specification.

- Boot SW: specification and prototype.

- IPs and HDSW: developed and validated on representative test equipment.

- ACE Interface Software: first version developed and under validation on test equipment including real HW for bus interface.

- OBSW EP: Real Time Operation System prototype under test on Virtual Platform.

Project is foreseen to be extended to cover the OBC-D FUMO manufacturing, HW SW integration and tests.