PAGE CONTENTS

Objectives

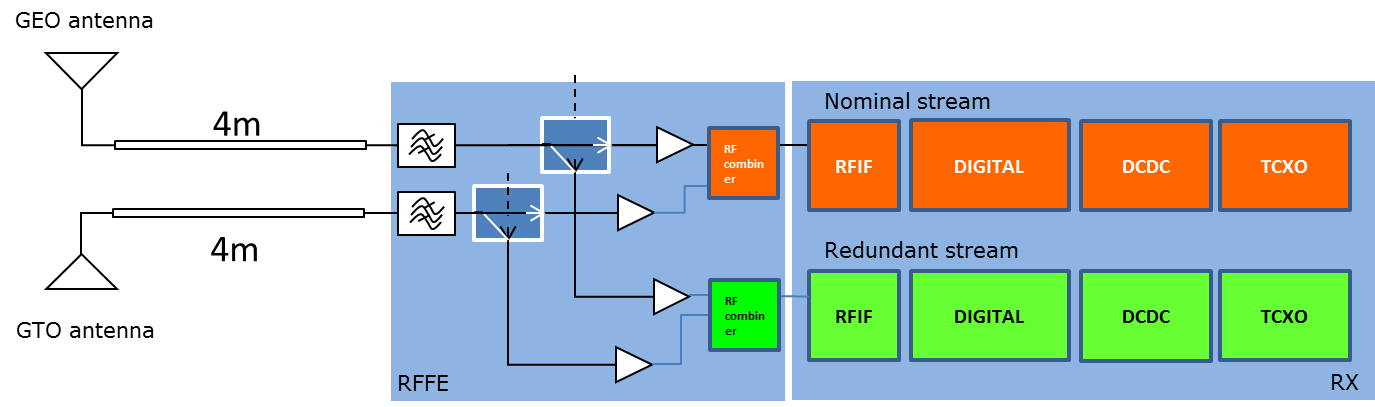

The availability of an autonomous mean of positioning in a geostationary platform is essential in reducing the dependence on the ground control, especially when low-thrust electrical propulsion is used to transfer the satellites to the GEO orbit, a manoeuvre that lasts several months. In this case, the on-board GNSS function can autonomously feed the avionic systems in charge of controlling the trajectory and the attitude, and schedule in this way the requested thrusters actuations and attitude variations.

Nowadays the use of GNSS Receivers in GEO satellites is a reality, although their cost is quite high. The first part of the project has been focused on the cost-wise analysis of the architecture of a GNSS receiver to identify the potential areas where a significant reduction of the recurring cost can be achieved.

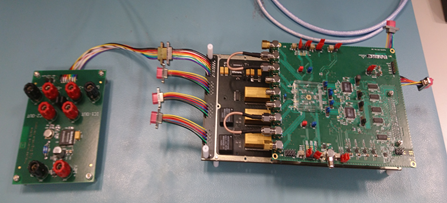

In the second part, a novel architecture of the RF-IF section of the receiver has been designed and manufactured using a highly integrated solution based on a hybrid RF-digital MMIC developed for this purpose in the frame of the project.

Finally an elegant breadboard incorporating both the RF-IF section and an AGGA-4-based digital board has been assembled and tested to verify the overall performance of the GNSS receiver.

Challenges

- Revisit current navigation receiver implementations for GEO satellites to define an architecture and physical implementation compatible with the target cost of 200 k€ for the final space qualified flight model.

- Develop an elegant breadboard implementing an innovative, highly integrated RF-IF section using a new hybrid RF-digital MMIC design.

System Architecture

The Elegant Breadboard designed and developed in the frame of the project consist of a RF-IF section, based on a highly integrated MMIC designed and manufactured ad hoc, and of a digital section based on AGGA-4 processor. These two sections represent the core elements of a GNSS receiver and allow to verify the overall performance.

Plan

The project started in May 2017 and is split into three phases.

Phase 1: architectural trade-off, receiver specifications and preliminary design. Phase 1 ended with Preliminary Design Review, held in November 2017

Phase 2: EBB detailed design (RF-IF board and digital board) and MMIC manufacturing. Phase 2 ended with Detailed Design Review, concluded in July 2018.

Phase 3: RF-IF Board manufacturing and test and EBB integration and performance test. Test Review Board held on June 2020.

The duration of phase 3 has been affected by the COVID-19 pandemic.

Current Status

The project has been completed.